一种时序精确的集成电路网络应用系统建模与仿真环境可以是基于硬件描述语言(HDL)和时序仿真器的软件工具。该环境可以用于对集成电路网络应用系统进行建模和仿真,以验证系统设计的正确性和性能。

以下是该环境的主要特点和功能:

硬件描述语言支持:该环境应支持常用的硬件描述语言,如VHDL(Very High-Speed Integrated Circuit Hardware Description Language)和Verilog,以便用户使用这些语言对集成电路网络应用系统进行建模和描述。

时序精确仿真:该环境应能够进行时序精确的仿真,即对电路中的时序逻辑进行精确的时钟周期级仿真。这样可以确保设计在实际工作条件下的正确性和稳定性。

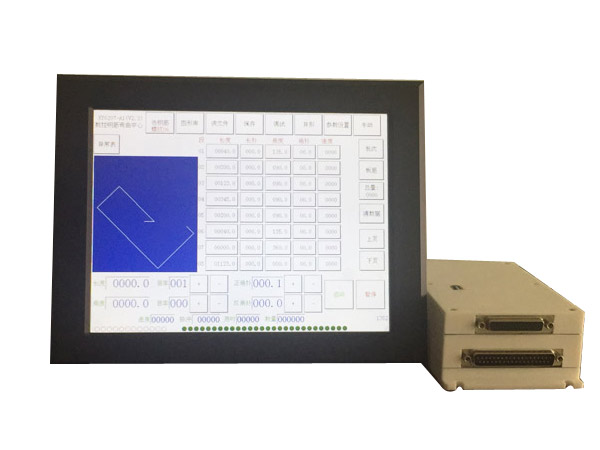

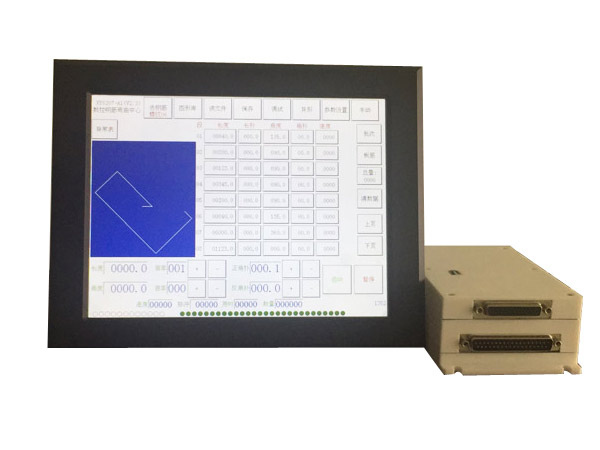

强大的仿真功能:该环境应具备完善的仿真功能,包括时钟和复位信号的生成、仿真时序的设置和控制、信号波形的显示和分析等。用户可以对仿真过程进行全面的控制和监控,以验证设计的功能和性能。

仿真波形可视化:该环境应提供直观的仿真波形可视化功能,以便用户查看和分析仿真结果。用户可以观察信号的变化、时序约束的满足情况、时序冲突等,从而判断设计是否满足系统要求。

错误检测和调试功能:该环境应具备错误检测和调试功能,能够帮助用户快速定位和解决设计中的问题。包括提供错误提示、断点设置、变量监视等功能,以便用户进行错误分析和调试。

高性能和高效率:该环境应具备高性能和高效率的仿真引擎,以支持大规模、复杂的集成电路网络应用系统的建模和仿真。同时,该环境应具备高效的仿真算法和优化技术,以提高仿真速度和准确性。

时序精确的集成电路网络应用系统建模与仿真环境对于电路设计和验证非常重要。它可以帮助设计人员在设计阶段发现和解决潜在的问题,提高设计的质量和可靠性。同时,该环境还可以加快设计周期,降低开发成本,提高工作效率。

冀公网安备 13100202000581号

冀公网安备 13100202000581号